(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 4, April 2016

# A Review on Vedic Multiplier using Reversible Logic Gate

Sonali S. Kothule<sup>1</sup>, Govind U. Kharat<sup>2</sup>, Shekhar H. Bodake<sup>3</sup>

P.G. Student, Department of E&TC, SP College of Engineering, Otur, Pune, Maharashtra, India<sup>1</sup>

Professor, Department of E&TC, SP College of Engineering, Otur, Pune, Maharashtra, India<sup>2</sup>

Assistant Professor, Department of E&TC, SP College of Engineering, Otur, Pune, Maharashtra, India<sup>3</sup>

**ABSTRACT**: System performance is decided by way of the speed of the multiplier, that is the most important element in the numerous of the application like Microprocessor, Digital signal processing, Quantum Computing etc. Multipliers have large area, long latency and devour huge energy. Hence suitable multiplier structure will increase the performance and overall efficiency of the system. The Vedic multiplier improves the speed of the computation and differing types of reversible gates is use to reduce the power consumption because having capability of reversible calculation that means no data loss take place. Reversible logic has wide application in the developing technologies such as quantum computing, optical computing, Nano-technology and so on. From the survey it is observed that the reversible Vedic multiplier is the pre-eminent in the terms of power, area, delay and quantum cost.

**KEYWORDS**: Vedic Multiplier, Reversible Logic, UrdhvaTiryakbhayam, Quantum Cost, power, delay.

### I. INTRODUCTION

Vedic mathematics is the earliest Indian system of mathematics which in particular offers with Vedic mathematical formulae and their application to numerous branches of mathematics. Vedic mathematics was reconstructed from the earliest Indian scriptures (Vedas) by Sri BharatiKrsnaTirtha after his study on Vedas. He created 16 sutras and 16 upa sutras after vast study in Atharva Veda. The maximum famous amongst those sixteen are NikhilamSutram, UrdhvaTiryakbhayam, and Anurupye. It has been found that UrdhvaTiryakbhayam is the maximum efficient among those. The splendor of Vedic mathematics lies in the fact that it decreases otherwise cumbersome looking calculations in traditional mathematics to quite simple ones. This is so because the Vedic sutras are claimed to be primarily based on the natural ethics on which the human thought works. Therefore multiplications in DSP blocks can be performed at faster rate. This is a completely interesting subject and affords a few powerful algorithms which can be applied to numerous branches of engineering [2].

Reversible logic has received excessive attention in the recent years due to their capacity to decrease the power dissipation which is the principle requirement in low power very large scale integration design. It has wide uses in low power complementary metal-oxide semiconductor and optical science, polymer computing, quantum computation and nanotechnology. Irreversible hardware working out results in energy dissipation due to data loss. [18]

Reversible logic is one of the encouraging fields for upcoming low power design technologies. Since one of the necessities of all digital signal processors and other hand held devices is to reduce power dissipation multipliers with excessive speed and lower dissipations are essential. [20]

### II. RELATED WORK

In 2011, Prashant .R.Yelekar, Prof. Sujata S. Chiwande [5], introduce reversible logic gates and its applications like Low power CMOS, Quantum computer, Nanotechnology, Optical computing, Design of low power arithmetic and data path for digital signal processing (DSP), Field Programmable Gate Arrays (FPGAs) in CMOS technology for extremely low power, high testability and self-repair.

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Issue 4, April 2016

In 2012, PushpalataVerma [11], designed the  $4\times4$  bit Vedic multiplier is implemented on Spartan xc3s50a-5-tq144 device. The computational path delay of the Vedic multiplier is found to be 13.102 ns. Hence it can be concluded that the performance of the proposed  $4\times4$  bit Vedic multiplier seems to be highly efficient in terms of speed when compared to Conventional multipliers. Reducing the time delay is very essential requirement for many applications and Vedic Multiplication technique is very much suitable for this purpose.

In 2013, Rakshith T.R. and RakshithSaligram [20], proposed the Vedic multiplier using reversible logic in Xilinx 9.2i and MODELSIM with reduced TRLIC and reduced delay.

In 2014, A. ShifanaParween, S. Murugeswari [18], design high speed, area efficient, low power vedic multiplier using reversible logic gate. They compare array multiplier and vedic multiplier using different parameters like no. of gate, number of slices, constant inputs, garbage output, delay, total equivalent gate count, power, quantum cost.

In 2015, Akanksha Kant, Shobha Sharma[19], presented different applications of vedic multiplier like in image compression using discrete cosign transform (DFT) algorithm, in multi-level 2D discrete wavelet transform (DWT) for image processing, in the design of low power asynchronous vedic DSP processor core, in parallel FIR filter, in the design of high speed ASIC design.

#### **III. VEDIC MATHEMATICS**

The word "Vedas" which literally means knowledge has derivational meaning as source and boundless store-house of all information. The word Veda as well refers to the sacred earliest Hindu literature that is split into four volumes. Vedas first of all had been surpassed from preceding generation to next generation orally. Later they were transcribed in Sanskrit. [3]

Vedas consist of statistics from many topics such as from religion, astronomy, construction, arithmetic, medication etc. Vedic mathematics isn't only a mathematical wonder however also it's miles logical. That is why Vedic mathematics has such a grade of importance which cannot be criticized. Due to these characteristics, Vedic mathematics has already crossed the boundaries of India and has become a leading topic of research overseas. Vedic mathematics deals with various mathematical operations.

The system of Vedic mathematics is based on 16 Sutras. [9] These Sutras along with their brief meanings are enlisted below alphabetically-

| No. | Sutras                          | Meanings                                            |

|-----|---------------------------------|-----------------------------------------------------|

| 1   | Shunyamanyat                    | If one is in ratio, the other is 0.                 |

| 2   | ChalanaKalanabyham              | Differences and similarities.                       |

| 3   | EkadhikinaPurvena               | By one more than the preceding one.                 |

| 4   | EkanyunenaPurvena               | By one less than the preceding one.                 |

| 5   | Gunakasamuchyah                 | Factors of the sum are equal to the sum of factors. |

| 6   | Gunitasamuchyah                 | The product of sum is equal to sum of the product.  |

| 7   | NikhilamNavatashcaramamDashatah | All from 9 and last from 10.                        |

| 8   | ParaavartyaYojayet              | Transpose and adjust.                               |

| 9   | Puranapuranabyham               | By the completion or non completion.                |

| 10  | Sankalanavyavakalanabhyam       | By addition and by subtraction.                     |

| 11  | ShesanyankenaCharamena          | The remainders by the last digit.                   |

| 12  | ShunyamSaamyasamuccaye          | When the sum is same then sum is 0.                 |

| 13  | Sopaantyadvayamantyam           | The ultimate and twice the penultimate.             |

| 14  | Urdhva-tiryakbhyam              | Vertically and crosswise.                           |

| 15  | Vyashtisamanstih                | Part and Whole                                      |

| 16  | Yaavadunam                      | Whatever the extent of its deficiency.              |

TABLE I

The 16 vedic sutras and their brief meanings

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 4, April 2016

#### IV. REVERSIBLE LOGIC GATE

Reversible circuits are those circuits that don't loose data. Reversible computation in a device can be executed best while the device consists of reversible gates. These circuits can generate specific output vector from every input vector, and vice versa, that is, there is a one-to-one mapping between input and output vectors. Thus, an  $N \times N$  reversible gate can be represented as

$$I_v = (I_1, I_2, I_3, I_4, \dots, I_N)$$

$O_{v} = (O_{1}, O_{2}, O_{3}, \dots, O_{N}).$

Where Iv and Ov represent the input and output vectors respectively.[5] The following are the vital design constraints for reversible logic circuits. [20]

- Reversible logic gates do not permit fan-outs.

- Reversible logic circuits should have smallest quantum cost.

- The design can be optimized so as to generate smallest number of garbage outputs.

- The reversible logic circuits must use smallest number of constant inputs.

- The reversible logic circuits must use a smallest logic depth or gate levels.

#### A. Basic Reversible Logic Gates[18]

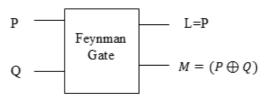

1) *Feynman gate*: Fig 1 shows a 2\*2 Feynman gate. The input vector is I (P, Q) and the output vector is O (L, M). The outputs are defined by L=P, M=P xor Q. Quantum cost of a Feynman gate is 1.

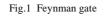

2) *Peres gate:* Fig 2 shows a 3\*3 Peres gate. The input vector is I (P, Q, R) and the output vector is O (L, M, N). The output is defined by L = P, M = P xor Q and N=PQ xor R. Quantum cost of a Peres gate is 4. In the proposed design Peres gate is used because of its lowest quantum cost.

Fig. 2 Peres gate

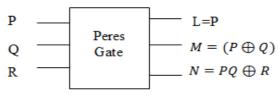

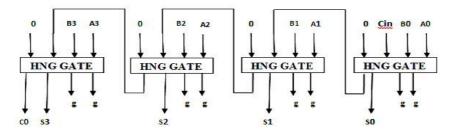

*3) HNG gate:*Fig 3 shows a HNG Gate. The input vector is I (P, Q, R, S) and the output vector is O (L, M, N, O).The full adder using HNG is obtained with R= Cin and S=0.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 4, April 2016

Fig. 3 HNG gate

#### V. VEDIC MULTIPLIER

UrdhvaTiryakbhayam (UT) is a multiplier primarily based on Vedic mathematical algorithms formulated by ancient Indian Vedic mathematicians. The "UrdhvaTiryagbhyam" Sutra is a preferred multiplication formula relevant to all cases of multiplication along with binary, hex, decimal and octal. The Sanskrit word "Urdhva" means "Vertically" and "Tiryagbhyam" means "crosswise". Fig 4 shows an example of UrdhvaTiryagbhyam. [3]

The partial products are generated parallel and simultaneous additions of the partial products are performed using this algorithm. Because of this the speed of the multiplier is improved significantly when compared to other procedures. [2]

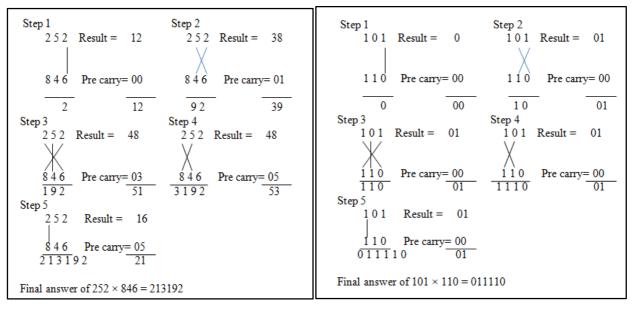

The Algorithm: Multiplication of 101 by 110. [20]

- 1. We will take the right-hand digits and multiply them together. This will give us LSB digit of the solution.

- 2. Multiply LSB digit of the top number by the second bit of the bottom number and the LSB of the bottom number by the second bit of the top number. Once we have those values, add them together.

- 3. Multiply the LSB digit of bottom number with the MSB digit of the top one, LSB digit of top number with the MSB digit of bottom and then multiply the second bit of both, and then add them all together.

- 4. This step is similar to the second step, just move one place to the left. We will multiply the second digit of one number by the MSB of the other number.

- 5. Finally, simply multiply the LSB of both numbers together to get the final product.

(a)

(b)

Fig. 4.UrdhvaTiryagbhyam algorithm (a) for decimal multiplication (b) binary multiplication

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Issue 4, April 2016

#### VI. VEDIC MULTIPLIER USING REVERSIBLE LOGIC

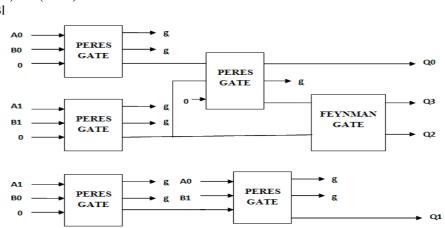

The 2 X 2 UrdhvaTiryagbhyam multiplier using conventional logic will have 4 outputs. The logical expressions are given below. [18]

Q0=A0.B0Ql=(A1.B0) xor (A0.Bl)

Q2= (A0.Al.B0.Bl) xor (Al.Bl) Q3= A0.Al.B0.Bl

Fig. 5 A 2 X 2 UrdhvaTiryagbhyam Multiplier Unit

The reversible logic implementation of the above expressions has need of four peres gate and one Feynmen (CNOT) gate. The reversible logic implementation of 2 X 2 UT multiplier is shown in the Fig 5. The quantum cost of the 2X2 UrdhvaTiryakbhayam Multiplier is found to be 21. The number of garbage outputs is 9 and number of constant inputs is 4.

Fig. 6 Four bit ripple carry adder using HNG gate

The partial products generated using the 2 X 2 UT multiplier are need to be added using the four bit adder. The four bit ripple carry adder unit was designed using the HNG reversible gate. The four bit ripple carry adder unit using HNG gate is shown in the Fig 6.

The quantum cost of 4 bit adder unit using HNG gate is 24. The number of garbage output is 8 and constant input is 4. [20]

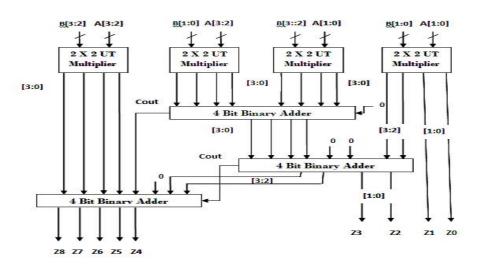

The architecture of 4 X 4 UrdhvaTiryagbhyam multiplier circuit is shown in the fig 7. It consist of four 2 X 2 UT multiplier unit and three 4 bit binary adders.

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 4, April 2016

Fig. 7 A 4X4 UT multiplier using reversible logic gate

#### VII. CONCLUSION

In this paper the vedic multiplier using reversible logic method have been discussed. As per study the speed of a multiplier is increases by using UrdhvaTiryagbhyam multiplier and the negligible power can be achieved by reversible logic gate.

This paper presents the UrdhvaTiryakbhayam Vedic Multiplier realized using reversible logic gates. First 2X2 UT multiplier is designed using Peres gate and Feynmen gate. The ripple carry adders which were required for adding the partial products were constructed using HNG gates.

#### REFERENCES

- Krishnaveni D., Umarani T.G., "VLSI implementation of Vedic multiplier with reduced delay", International Journal of Advanced Technology & Engineering Research (IJATER) National Conference on Emerging Trends in Technology (NCET-Tech), Vol. 2, Issue 4, July 2012.

- [2] Poornima M, Shivaraj Kumar Patil, Shivukumar , Shridhar K P , Sanjay H, "Implementation of Multiplier using Vedic Algorithm", International Journal of Innovative Technology and Exploring Engineering (IJITEE), Vol.2, Issue 6, May 2013.

- [3] G.Vaithiyanathan, K.Venkatesan, S.Sivaramakrishnan, S.Siva, S. Jayakumar, "Simulation and implementation of Vedic multiplier using VHDL code", International Journal of Scientific & Engineering Research, Vol. 4, Issue 1, January-2013.

- [4] Premananda B.S., Samarth S. Pai, Shashank B., Shashank S. Bhat, "Design and Implementation of 8-Bit Vedic Multiplier", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 2, Issue 12, December 2013.

- [5] Prashant R. Yelekar, Prof. Sujata S. Chiwande, "Introduction to Reversible Logic Gates & its Application", proc.2nd National Conference on Information and Communication Technology (NCICT) in International Journal of Computer Applications® (IJCA)(2011).

- [6] B. Raghukanth, B. Murali Krishna, M. Sridhar, V.G. SanthiSwaroop, "A distinguish between reversible and conventional logic gates", International Journal of Engineering Research and Applications (IJERA), Vol. 2, Issue 2, pp.148-151, Mar-Apr 2012.

- [7] PrabirSaha, Arindam Banerjee, Partha Bhattacharyya, AnupDandapat, "High Speed ASIC Design of Complex Multiplier Using Vedic Mathematics," Proc.IEEE, 2011.

- [8] ManoranjanPradhan, Rutuparna Panda, Sushanta Kumar Sahu, "Speed Comparison of 16×16 Vedic Multipliers", International Journal of Computer Applications, Volume 21–No.6, May 2011.

- [9] G. Ganesh Kumar, V. Charishma, "Design of High Speed Vedic Multiplier using Vedic Mathematics Techniques", International Journal of Scientific and Research Publications, Volume 2, Issue 3, March 2012.

- [10] Ramachandran.S, Kirti.S.Pande, "Design, Implementation and Performance Analysis of an Integrated Vedic Multiplier Architecture", IJCER, Vol. 2, Issue No.3 PP.697-703, May-June 2012.

- [11] PushpalataVerma, "Design of 4×4 bit Vedic Multiplier using EDA Tool", International Journal of Computer Applications, Volume 48– No.20, June 2012.

- [12] M. Nagaraju, R. Surya Prakash, B. Vijay Bhaskar, "High Speed ASIC Design of Complex Multiplier Using Vedic Mathematics", International Journal of Engineering Research and Applications (IJERA), Vol. 3, Issue 1, pp.1079-1084, January -February 2013.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 4, April 2016

- [13] R. Sridevi, AnirudhPalakurthi, AkhilaSadhula, HafsaMahreen, "Design of a High Speed Multiplier (Ancient Vedic Mathematics Approach)", International Journal of Engineering Research, Volume No.2, Issue No.3, pp : 183-186 01 July 2013.

- [14] T. Naga Babu, D.Sounder, B.SubhakaraRao, P. Bose Babu, "A low power adder using reversible logic gates", IJRET, Vol.1, Issue 3, pp.244 247, Nov 2012.

- [15] NeelamArya, Priyanka Mishra, Shweta Singh, "Reversible Vedic Multiplier", [Online document], 5September2012, Available: http://www.manishapattanaik.in/report/reversiblevedicmultiplier.

- [16] PushpalataVerma, K. K. Mehta, "Implementation of an Efficient Multiplier based on Vedic Mathematics Using EDA Tool", International Journal of Engineering and Advanced Technology (IJEAT), Vol.1, Issue 5, June 2012.

- [17] Manjeet Singh Sankhwar, Rajesh Khatri, "Design of High Speed Low Power Multiplier Using Nikhilam Sutra with Help of Reversible Logic", International Journal Of Modern Engineering Research (IJMER), vol. 4, Issue 1,pp.159-167, Jan. 2014.

- [18] A. ShifanaParween, S. Murugeswari, "Design of High Speed, Area Efficient, Low power Vedic Multiplier using Reversible Logic Gate ", International Journal of Emerging Technology and Advanced Engineering, Volume 4, Issue 2, February 2014.

- [19] Akanksha Kant, Shobha Sharma, "APPLICATIONS OF VEDIC MULTIPLIER DESIGNS A REVIEW", IEEE, 2015.

- [20] Rakshith T. R., RakshithSaligram, "Design of high speed low power multiplier using reversible logic: A Vedic mathematical approach", IEEE, 2013.